|

Логика Электронное учебное пособие |

|

|

Сумматор двоичных чисел

Логические схемы имеют практическое применение в вычислительной технике. Они используются:

1. Для реализации выполнения математических операций. Свое название («компьютер») компьютер получил не сразу. Сначала данное устройство называлось электронно-вычислительная машина, т.е. одним из главных назначений ЭВМ было выполнение вычислительных операций. Занималось этим специальное устройство, которое называется процессор. Процессор можно сравнить с умом человека. И именно процессор (так же, как и человек в «уме») выполнял (и выполняет) все математические операции. Рассмотрим как он это делает.

2. Для хранения информации.

Итак, как процессор выполняет математические операции?

Прежде всего, ответьте на вопросы:

- Каким образом должна быть представлена информация, чтобы с ней мог работать компьютер?

- Чтобы компьютер мог выполнять математические операции с числами, в какой системе счисления они должны быть представлены?

- Почему?

- Какие сигналы подаются на входы логических вентилей?

Вывод: таким образом и в двоичной системе счисления и в алгебре логики информация представлена в виде двоичных кодов.

И второй момент. Для того чтобы максимально упростить работу компьютера, все математические операции (вычитание, деление, умножение и т.д.) сводятся к сложению.

Вспомним таблицу сложения двоичных чисел. Запишем ее в несколько иной форме.

|

A |

B |

|

S |

|

0 |

0 |

|

0 |

|

0 |

1 |

|

1 |

|

1 |

0 |

|

1 |

|

1 |

1 |

1 |

0 |

Обратите внимание на дополнительный столбец. Его мы ввели потому, что при сложении происходит перенос в старший разряд. Обозначим его Р и закончим заполнение таблицы.

|

A |

B |

P |

S |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

Проанализируем полученный результат.

- Таблице истинности какой логической функции аналогичен столбец P? (Логическое умножение.)

- Таблице истинности какой логической функции аналогичен столбец S? (Логическое сложение, кроме случая, когда на выходы подаются две единицы.)

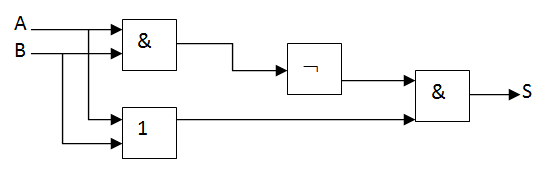

Логическое выражение, по которому можно определить сумму S, записывается следующим образом: S=(AvB)& ¬(A&B).

Построим к этому логическому выражению логическую схему:

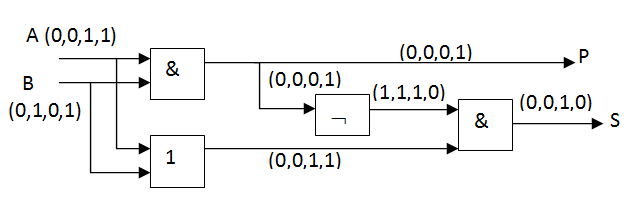

Проследим за изменением сигнала при прохождении через схему:

- С какого элемента можно снимать сигнал P, если мы выяснили, что результат P соответствует логическому умножению? (С первого вентиля, реализующего операцию конъюнкции.)

Полученная нами схема выполняет сложение двоичных одноразрядных чисел и называется полусумматором, так как не учитывает перенос из младшего разряда в старший (выход P).

Для учета переноса из младшего разряда необходимы два сумматора. Более «умным» является устройство, которое при сложении учитывает перенос из младшего разряда. Называется оно полный одноразрядный сумматор.

Сумматор – это логическая электронная схема, выполняющая сложение двоичных чисел. Сумматор является главной частью процессора.

Рассмотрим принцип работы одноразрядного двоичного сумматора.

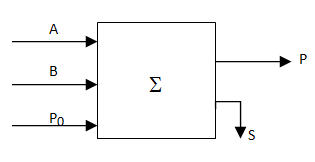

Одноразрядный сумматор должен иметь три входа: А, В – слагаемые и Р0 – перенос из предыдущего разряда и выходы: S – сумма и Р – перенос.

Нарисуем одноразрядный сумматор в виде единого функционального узла:

|

|

|

A |

B |

P0 |

P |

S |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Логические выражения для P и S будут иметь следующий вид:

S=(AvBvP0)& ¬ P0v(A&B&P0)

P=(A&B)v(A&P0)v(B&P0)

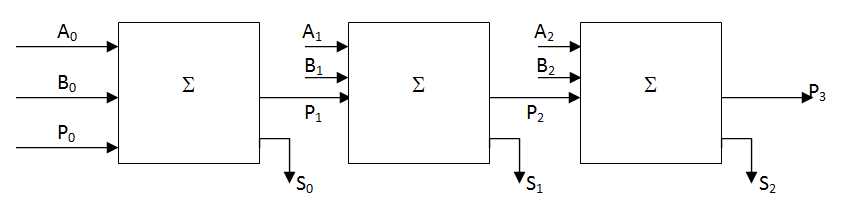

Но процессор, как правило, складывает многоразрядные двоичные числа. Например, 1012+1102=10112. Для того чтобы вычислить сумму n-разрядных двоичных чисел, необходимо использовать многоразрядный сумматор, в котором на каждый разряд ставится одноразрядный сумматор и выход-перенос сумматора младшего разряда подключается к входу сумматора старшего разряда.